- 您现在的位置:买卖IC网 > Sheet目录1994 > DS21Q58L (Maxim Integrated Products)IC TXRX E1 QUAD 3.3V 100-LQFP

DS21Q58 E1 Quad Transceiver

29 of 74

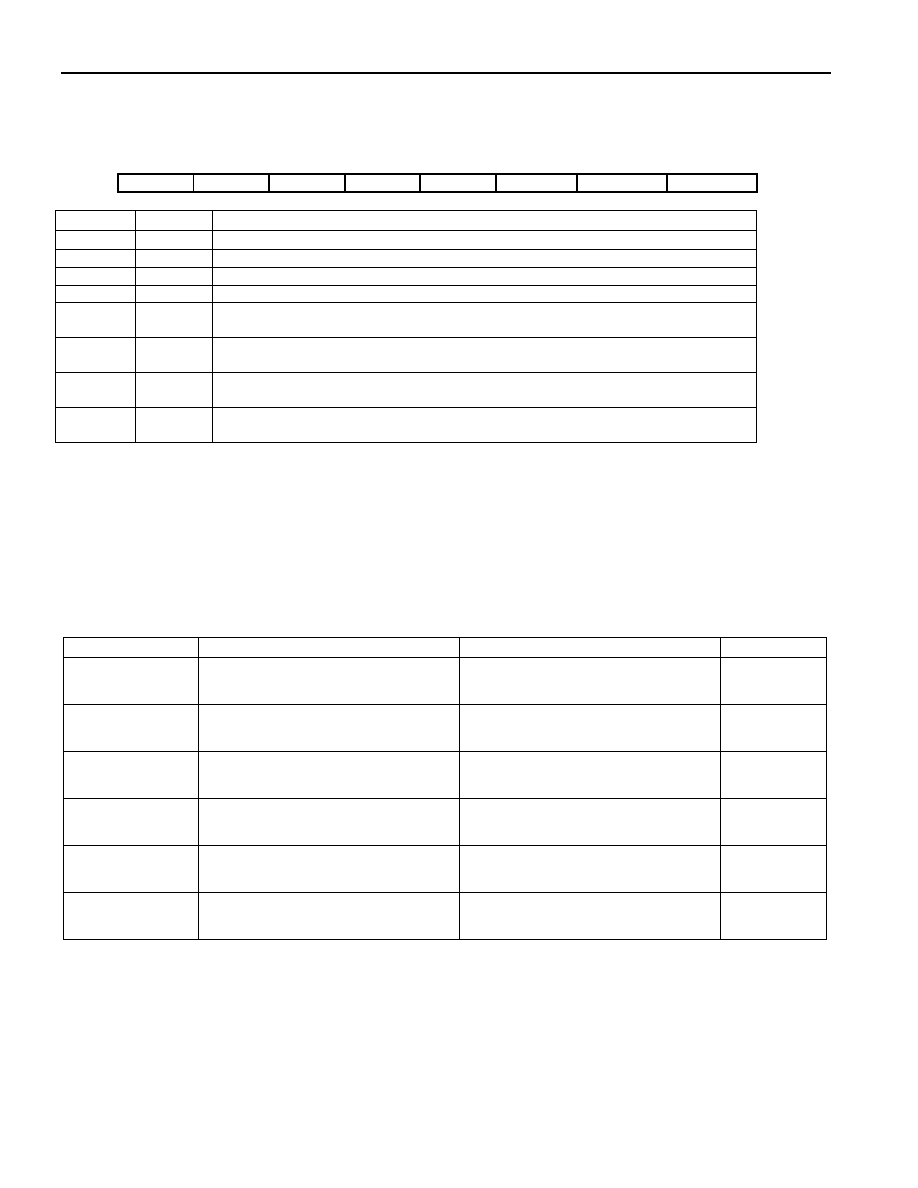

Register Name:

SSR

Register Description:

Synchronizer Status Register

Register Address:

09 Hex

Bit #

7

6

5

4

3

2

1

0

Name

CSC5

CSC4

CSC3

CSC2

CSC0

FASSA

CASSA

CRC4SA

NAME

BIT

FUNCTION

CSC5

7

CRC4 Sync Counter Bit 5. MSB of the 6-bit counter.

CSC4

6

CRC4 Sync Counter Bit 4

CSC3

5

CRC4 Sync Counter Bit 3

CSC2

4

CRC4 Sync Counter Bit 2

CSC0

3

CRC4 Sync Counter Bit 0. LSB of the 6-bit counter. Counter bit 1 is not

accessible.

FASSA

2

FAS Sync Active. Set while the synchronizer is searching for alignment at the

FAS level.

CASSA

1

CAS MF Sync Active. Set while the synchronizer is searching for the CAS MF

alignment word.

CRC4SA

0

CRC4 MF Sync Active. Set while the synchronizer is searching for the CRC4

MF alignment word.

9.2 CRC4 Sync Counter

The CRC4 sync counter increments each time the 8ms CRC4 multiframe search times out. The counter is cleared

when the framer has successfully obtained synchronization at the CRC4 level. The counter can also be cleared by

disabling the CRC4 mode (CCR1.0 = 0). This counter is useful for determining the amount of time the framer has

been searching for synchronization at the CRC4 level. ITU G.706 suggests that if synchronization at the CRC4

level cannot be obtained within 400ms, the search should be abandoned and proper action taken. The CRC4 sync

counter rolls over.

Table 9-1. Alarm Criteria

ALARM

SET CRITERIA

CLEAR CRITERIA

ITU SPEC

RSA1

(Receive Signaling

All Ones)

Over 16 consecutive frames (one full

MF) time slot 16 contains less than three

zeros

Over 16 consecutive frames (one full

MF) time slot 16 contains three or more

zeros

G.732

4.2

RSA0

(Receive Signaling

All Zeros)

Over 16 consecutive frames (one full

MF) time slot 16 contains all zeros

Over 16 consecutive frames (one full

MF) time slot 16 contains at least a

single one

G.732

5.2

RDMA

(Receive Distant

Multiframe Alarm)

Bit 6 in time slot 16 of frame 0 set to one

for two consecutive MF

Bit 6 in time slot 16 of frame 0 set to

zero for two consecutive MF

O.162

2.1.5

RUA1

(Receive Unframed

All Ones)

Fewer than three zeros in two frames

(512 bits)

More than two zeros in two frames (512

bits)

O.162

1.6.1.2

RRA

(Receive Remote

Alarm)

Bit 3 of nonalign frame set to one for

three consecutive occasions

Bit 3 of nonalign frame set to zero for

three consecutive occasions

O.162

2.1.4

RCL

(Receive Carrier

Loss)

255 (or 2048) consecutive zeros

received

In 255-bit times at least 32 ones are

received

G.775/

G.962

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS2404B

IC ECONORAM TIMECHIP 5.5V 16SSOP

DS2415P+T&R

IC TIME CHIP 1-WIRE 6-TSOC

DS2417X/T&R

IC TIMECHIP W/INTRPT 1WIRE CSP

DS26502LN+

IC T1/E1/J1 64KCC ELEMENT 64LQFP

DS26503LN+

IC T1/E1/J1 BITS ELEMENT 64-LQFP

DS3105LN+

IC TIMING LINE CARD 64-LQFP

DS3106LN+

IC TIMING LINE CARD 64-LQFP

DS3231MZ+

IC RTC I2C 8SOIC

相关代理商/技术参数

DS21Q58L+

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q58LN

功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q58LN+

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q59

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:RELIABILITY REPORT FOR DS21Q59, REV A2

DS21Q59DK

功能描述:网络开发工具 DS21Q59 Dev Kit RoHS:否 制造商:Rabbit Semiconductor 产品:Development Kits 类型:Ethernet to Wi-Fi Bridges 工具用于评估:RCM6600W 数据速率:20 Mbps, 40 Mbps 接口类型:802.11 b/g, Ethernet 工作电源电压:3.3 V

DS21Q59L

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q59L+

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

DS21Q59LN

功能描述:网络控制器与处理器 IC Quad E1 Transceiver RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray